Quantum

computing

Building the computer of the future

Quantum computers have the potential to perform extremely complex calculations, by encoding information into quantum states. This opens the way for revolutionary applications, such as complex optimization challenges or prediction, simulation, and modelling of the behaviour of molecules, catalysts, and new materials.

Realizing the promise of quantum computing requires the development of different layers of hardware and software. Together, these layers are referred to as the quantum computing stack. This stack is what we explore at QuTech. The base of the stack – the ‘quantum processor’ – contains the qubits. We are investigating different types of qubits, along with the system architecture that translates quantum algorithms into electronic signals that operate on the qubits.

Quantum processors based on semiconductor technology

Long-term goal:

To build a modular spin-qubit processor for scalable quantum information processing.

Highlights

We demonstrated operating semiconductor quantum processors with hopping spins (Science). This work constitutes the first realisation of qubit operation as envisaged in the seminal work of quantum computation with quantum dots by Loss and DiVincenzo. We showed high-fidelity one and two-qubit gates in germanium, all with baseband control.

We kept advancing the state of the art in quantum-engineered semiconductors for spin-qubits by exploring strained germanium quantum wells with thick silicon-germanium barriers and strained silicon quantum wells with optimised quantum well thickness. As a result, using holes in germanium, we achieve a mobility of 4.7×106 cm2/Vs, the highest mobility ever measured in the industrially relevant group IV semiconductors (Appl. Phys. Lett.). For electrons in silicon, we take a co-design approach to the material stack, strike the delicate balance between disorder, charge noise, and valley splitting and demonstrate a large mean valley splitting energy of 0.24(7) meV, setting a benchmark for silicon as a host semiconductor for quantum dot qubits (npj Quantum Information).

We have realised a 4x2 Ge/SiGe quantum dot array containing eight hole spins, encoding four singlet-triplet qubits. This type of qubit can be controlled by just using baseband pulses only, removing the need for microwave signals. We achieved universal and high-fidelity control of the four qubits and were able to realise an entangled state of the first and last qubit in the array through a sequence of quantum operations that required all eight spins to remain quantum coherent (Nature Nanotechnology).

In another 4x2 Ge/SiGe quantum dot array, we demonstrated the formation and propagation of weakly bound electron-hole pairs, also called excitons. The exciton formation originates from the Coulomb interaction between opposite charges in nearby quantum dots. A ‘missing’ charge carrier on one site thereby attracts a (opposite) charge in a nearby site. Using the gate voltage, the ‘missing’ charge was controllably pushed forward, and we observed the accompanying opposite charge was being dragged along (Phys. Rev. X).

In a 28Si/SiGe heterostructure, we fabricated a hybrid device containing a NbTiN superconducting resonator of about 250 micron long, with a double quantum dot connected to both ends of the resonator. We placed one single electron in each double dot and tuned the device to a condition where both electron spins are resonant with each other but slightly detuned from the resonator. We engineered both spins to interact with the resonator, which results in an indirect interaction between the two distant spins, mediated by virtual photons in the resonator. We were able to control the time evolution of the two spins in such a way that energy was transferred coherently back and forth, corresponding to so-called iSWAP-oscillations. By proper timing, this corresponds to an entangling gate between two qubits 250 micron apart, about 1000 times farther apart than in conventional two-qubit gate implementations for spin qubits in quantum dots. We envision that this could be a route to creating on-chip networks of spin qubit registers (Nature Physics).

We demonstrated a method for autonomous operation of semiconductor quantum dots and virtualisation (Phys. Rev. X). We show a process for automated virtualisation of plunger and barrier control in a two-dimensional array of 10 quantum dots in germanium.

We demonstrated single-hole occupancy of stacked quantum dots (Appl. Phys. Lett.). Utilising double quantum wells in a Ge/SiGe heterostructure and electrostatic gate control, we show that it is possible to define quantum dot arrays extending the vertical direction. This work may constitute a path toward quantum dot systems beyond two dimensions for quantum simulation and computation.

We demonstrated that spin qubits can be shuttled through quantum dots (Nature Communications). Shuttling is a compelling method to establish quantum links between distant qubits, and this work represents a first step and understanding of the construction of such links in germanium.

Quantum processors based on superconducting technology

Long-term goal:

To realise an error-protected logical qubit with a superconducting circuit and a flexible control stack that also enables NISQ applications.

Highlights

In 2024, an upgrade of the superconducting backend of Quantum Inspire, from the original Starmon-5 to Starmon-7, was set in motion. Despite the modest increase in qubit count, the number of connected qubit pairs doubled, and the speed and/or fidelity of quantum operations (particularly readout) improved. We worked with the Quantum Inspire web-team and solved important system integration related challenges both at the level of quantum software, cloud connection and ICT infrastructure.

The Starmon-7 systems were ultimately released alongside the upgraded Quantum Inspire 2.0 software platform in Q1 2025. As scientific highlight and use case, we have studied the impact of ionising radiation (e.g., cosmic rays and local radioactivity) on both Starmon-5 and Starmon-7. We have identified key differences in the response of these processors to the radiation, which we link to the different types of Josephson junctions they employ (Dolan- versus Manhattan-style). A manuscript presenting these results will be finalised by Q2 2025.

2024 involved a much deeper transformation in our effort to scale superconducting quantum processors for both scientific research in quantum error correction and public access. Funded by QDNL (project HectoQubit/2) and the European Flagship on Quantum Technologies (project OpenSuperQ+), we have strengthened the collaboration with spin-off companies QuantWare (quantum hardware), Delft Circuits (cryogenic cabling), Qblox (control electronics), and Orange Quantum Systems (calibration software and quantum operating system) in pursuit of a publicly available 100-qubit processor capable of error correction by Q3 of 2026. In this effort, QuTech acts as system integrator of all layers of the quantum computer.

To give an example, QuTech designs quantum processors at the Hamiltonian level and tests prototype devices laid out and fabricated by QuantWare, providing key feedback for fast iteration. Similar entanglements are in place with all other partners, who have improved their products or brought new ones to market as a result. A scientific highlight of this effort in 2024 was using the HectoQubit prototype system Tuna-5 to investigate the optimal biasing of tuneable couplers to mitigate quantum sources of crosstalk during quantum operations. A manuscript on this work was finalised in Q1 of 2025 (ArXiv) and submitted. Furthermore, the Tuna-5 system would eventually go public on the Quantum Inspire platform in Q2 of 2025.

In error correction, we demonstrated, in collaboration with Riverlane, the advantage of using soft measurement information in decoding, and thus stabilising, a logical qubit encoded in 13 transmon qubits of a superconducting chip (Phys. Rev. Appl.). Decoding using soft information is widely applicable, independent of the physical qubit platform, and could allow for shorter readout durations, minimising logical error rates.

Cryogenic electronics

Long-term goal:

To replace room-temperature electronics that control quantum processors with integrated cryogenic electronics, operating near the qubits, to facilitate large-scale quantum computers.

Highlights

We presented the first cryo-CMOS quantum controller for color-centre qubits in diamond, enabling modular 3D integration of photonics, cryo-CMOS electronics, and qubits. Scalable quantum operations face challenges such as low coil-to-qubit coupling—requiring large drive currents—and the need for active Larmor frequency calibration. To address these, we proposed a cryo-CMOS system comprising a class-DE series-resonant AC driver and a triode-biased H-bridge DC current regulator. Validated using a nitrogen-vacancy (NV) qubit, the AC driver achieved 2.5 MHz Rabi oscillations at 6.5 mA supply current, while the regulator tuned the Larmor frequency by ±9 MHz with ±20 mA coil current. Using Ramsey experiments and gate set tomography, we demonstrated single-qubit gate fidelities above 98%. These results highlighted the potential of cryo-CMOS for scalable, low-power quantum control in modular color-centre architectures (IEEE Journal).

RF gate-based readout is a promising approach for scalable spin qubit systems, enabling fast, frequency-multiplexed measurements of multiple qubits. This work presents a theoretical framework to analyse how probe power, readout chain noise, and integration time affect signal-to-noise ratio and readout fidelity. By modelling the quantum dynamics of spin qubits during measurement, we provide a tool to evaluate trade-offs among key design parameters. The model is validated through simulation and experimental results, offering a practical method to optimise RF readout chains for faster, lower-power operation with integrated cryogenic electronics (IEEE Journal).

We demonstrated the first PAM4 wireline transmitter (TX) operating at cryogenic temperatures, addressing the need for high-speed data links between quantum processors at 4 K and classical processors at room temperature. As large-scale quantum computers rely on continuous quantum error correction, fast and efficient data transfer is critical. The proposed 40-nm CMOS TX integrates a low-power 64:4 serialiser, a 4:1 current-mode logic multiplexer, and a linear 6-bit DAC, optimised for cryogenic operation. It achieves 40 Gb/s (36 Gb/s) with 2.46 pJ/b (2.47 pJ/b) energy efficiency and 97.8% (96.6%) RLM at 4 K (RT), demonstrating performance comparable to advanced-node TXs at room temperature while supporting scalable quantum architectures (IEEE Journal).

Continuous quantum error correction (QEC) cycles are critical for realising fault-tolerant quantum computers (QCs). Each QEC round requires the rapid readout of thousands of ancilla qubits, faster than their decoherence times. To meet this demanding requirement, we introduced a cryogenic receiver for RF reflectometry-based readout of spin qubits. The proposed receiver advances the state of the art by incorporating a wideband passive amplification stage at the front end, effectively minimising the shot noise contribution of subsequent active components. This approach achieved a ~2.7× reduction in noise temperature compared to prior solutions and demonstrated high receiver performance in an RF reflectometry qubit readout setup—without relying on off-the-shelf low-noise amplifiers (LNAs) preceding the receiver (IEEE).

Several memories with different requirements are needed in the cryogenic controller of quantum processors. In a separate study, we benchmarked custom cryo-CMOS SRAM and DRAM, resulting in identification of specific cryogenic-aware design techniques and demonstrating significant performance and lower power dissipation at cryogenic temperature (IEEE).

Voltage references are fundamental in any electronic system. To use them in cryo-CMOS integrated circuits, we designed and statistically demonstrated the most accurate cryo-CMOS voltage references (IEEE).

Our first systematic analysis of the low-frequency noise in cryo-CMOS transistors suggests that, as no consistent decrease of such noise at lower temperatures is observed while the white noise is reduced, the impact of low-frequency noise for precision analog design at cryogenic temperatures gains a more predominant role. (IEEE)

Quantum computing architecture stack

Long-term goals:

To develop a scalable quantum computing control system stack that bridges the gap between quantum applications and quantum devices.

Highlights

We introduced the lightcone bound, a fundamental lower limit on quantum circuit mapping overhead derived from quantum information principles. Next, we developed a graph-based initial qubit placement algorithm validated across 600 realistic benchmarks, offering the first practical application of quantum circuit uncomplexity to near-term quantum computing (npj Quantum Information).

We developed beSnake, a fast and noise-aware qubit routing algorithm for scalable spin-qubit architectures, leveraging both SWAP and shuttle operations to optimise execution fidelity and time, achieving up to 80% reduction in gate overhead and over 8x speedup compared to existing methods on circuits with up to 1000 qubits (IEEE).

We introduced KetGPT, a Transformer-based tool for augmenting quantum circuit datasets with realistic, algorithm-inspired synthetic circuits in OpenQASM, enabling scalable benchmark generation and advancing the development of AI-driven quantum compilers (Computational Science).

We provided an overview of how full-stack quantum computing systems are currently being implemented and discussed the main challenges in transitioning from the current state to a comprehensive framework that supports fully automated, system-wide architecture, design, simulation, verification, and testing (IEEE).

Theory for assessing performance of quantum processors

Long-term goal:

To provide analyses and ideas towards implementing and assessing the performance of quantum error correction for superconducting and spin qubits.

Highlights

We showed how to optimise the parity check measurements of a wide class of quantum codes using ‘morphing’ circuits (Phys. Rev. Lett.). Our methods generated circuits which require fewer couplers-per-qubit, have built-in data-to-ancilla qubit swapping for leakage reduction, and offer the possibility of running parity checks via ISWAP instead of CZ gates. We demonstrated constructions which are as good as the best recent quantum LDPC codes (bivariate bicycle codes which can have 1/10 of the qubit overhead as compared to the surface code), plus have all these advantages. Our morphing framework is applicable to many codes, and it can also be used to generalise recently introduced methods for working around on-chip defective qubits and couplers.

To build a modular architecture, coherent links are required. We predicted theoretically that spins can be shuttled with high fidelity even in large spin-orbit fields typical of current devices (PRX Quantum). In collaboration with EPFL, we took the first steps toward enabling a spin-photon interface between quantum dots and superconducting resonators in planar Germanium (Nature Communications). We also showed theoretically that in this material system superconductors can mediate high-fidelity two-qubit gates between distant spins (Phys. Rev. B ).

To be able to scale a quantum processor, the fundamental building block - the qubit - must be well understood and reliably controlled. We developed a modelling framework for predicting the properties of hole spin qubits and predicted theoretical sweet spots. However, our analysis also revealed that such sweet spots are unique for each qubit, and averaging over multiple realisation reduces the emergence of such sweet spots (npj Quantum Information).

Quantum Inspire: the multi hardware quantum technology platform

Long-term goals:

To develop a full-stack quantum computer demonstrator for training and education, along with co-development and collaborative R&D of quantum technologies for quantum computing.

Highlights

Early in the year QuTech announced the formation of the HectoQubit/2 consortium, uniting with four Delft-based quantum companies to build full superconducting quantum computing systems to be made publicly available through Quantum Inspire. HectoQubit/2 is a critical first step on the path towards the development of a 100-qubit quantum computer in Delft as planned within the European Flagship consortium OpenSuperQPlus.

At the 2025 Quantum Computing for Industry and Public Sector (QCIP) event in Delft, Eduardo Reck Miranda, Composer and Professor of Computer Music at the University of Plymouth, together with two musicians, performed the quantum computer music piece Kwantumwerk on Quantum Inspire.

A large part of 2024 was dedicated to preparing for the launch of Quantum Inspire 2.0, which took place early 2025. On the software side, Quantum Inspire 2.0 offers users new quantum compilers and support for Qiskit and PennyLane. On top of that, it has a new functionality that users can use to integrate quantum and classical computing. On the hardware side, both a new superconducting qubit (Starmon-7) and a spin qubit quantum computer (Spin 2+) were introduced

The team also prepared for the launch of the MOOC by QTIndu, dedicated to Quantum Inspire: Quantum Hardware and its Applications with Quantum Inspire. Many high-quality teaching videos were recorded.

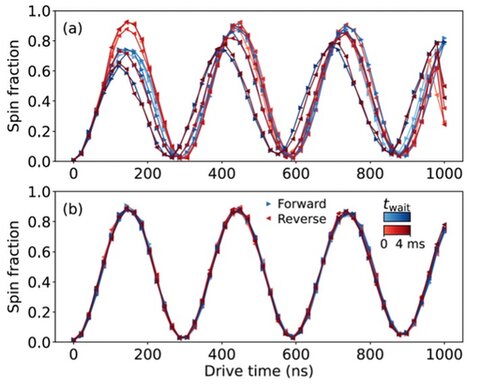

Figure: Rabi oscillations of a single electron spin at 12 mK (top) and 200 mK (bottom). The oscillations are taken with different wait times between single-shot measurements (see color bar) and scanning the drive time either from left to right, or the other way around. Heating effects cause major differences between these conditions when working at 12 mK. Remarkably, all curves fall on top of each other at 200 mK. Graphs reproduced from Phys. Rev. X.

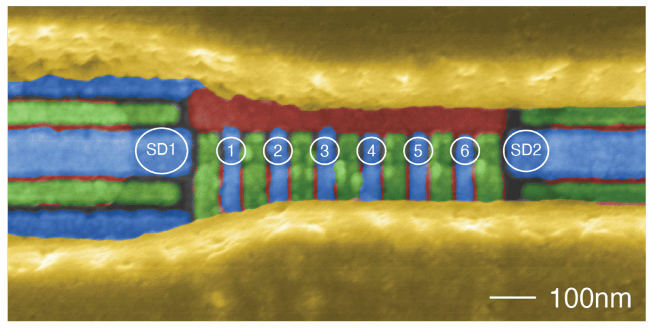

Image of the six-qubit quantum processor described in this article (Nature). The qubits are created by tuning the voltage on the red, blue, and green wires on the chip. The structures called SD1 and SD2 are extremely sensitive electric field sensors, which can even detect the charge of a single electron. These sensors together with advanced control schemes allowed the researchers to place individual electrons at the locations labeled (1)-(6), which were then operated as qubits.