Quantum

computing

Building the computer of the future

Quantum computers have the potential to perform extremely complex calculations, by encoding information into quantum states. This opens the way for revolutionary applications, such as complex optimization challenges or prediction, simulation, and modelling of the behaviour of molecules, catalysts, and new materials.

Realizing the promise of quantum computing requires the development of different layers of hardware and software. Together, these layers are referred to as the quantum computing stack. This stack is what we explore at QuTech. The base of the stack – the ‘quantum processor’ – contains the qubits. We are investigating different types of qubits, along with the system architecture that translates quantum algorithms into electronic signals that operate on the qubits.

Quantum processors based on semiconductor technology

Long-term goal:

To demonstrate prototypes of scalable quantum processors by exploiting semiconductor technology

Highlights

We pioneered semiconductor qubits based on silicon and germanium, obtaining key insights and methods. Quantum processors will require methods to scale to large numbers of qubits, as well as a high level of uniformity. We demonstrated shared control in a crossbar array, allowing to operate a record number of 16 quantum dots (Nature Nano.). For silicon, we achieved state-of-the-art material in terms of disorder, charge noise, and valley splitting (Nature Comm.). For germanium qubits, we introduced quantum wells grown on germanium wafers exhibiting a very high quality (Appl. Phys. Lett.). We also introduced electrical methods to improve uniformity and developed stress-voltage protocols that enabled to achieve single-electron occupancy in quantum dot arrays at a common gate voltage (Nano Letters and Nano Letters).

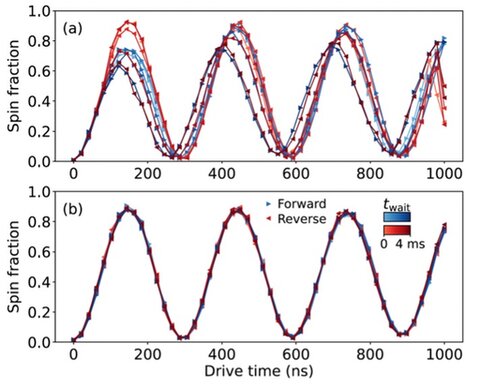

Quantum processors will also require high-fidelity and stable operation. Remarkably, we observed that qubit operation at 200mK can be more robust, as we found that it can mitigate the impact of heating due to microwave driving (Phys. Rev. X).

We demonstrated single qubit gate fidelities of 99.99% (Nature Comm.) and demonstrated singlet-triplet qubits and precise multi-spin control, enabling to perform the first quantum simulation with standard semiconductor materials (npj Quantum Information). We furthermore developed a framework for qubit control optimization (Quantum Sci. Technol.). In order to achieve quantum links that can couple remote qubits, we demonstrated shuttling of a single electron through an array of four quantum dots with errors below 0.01% (PRX Quantum). We observed transitions between excited states in the Jaynes-Cummings ladder of circuit quantum electrodynamics with electron spins, clarifying unexplained features from our 2018 Science paper (Phys. Rev. Lett.).

Quantum processors based on superconducting technology

Long-term goal:

To realize an error-protected logical qubit with a superconducting circuit and a flexible control stack that also enables NISQ applications.

Highlights

On the fabrication side, we performed a detailed investigation of the spatial uniformity of Josephson junctions at both wafer scale and die level, discerning the sensitivity of two junction fabrication processes to geometrical effects during electrode deposition (Quantum Sci. Technol.). We also demonstrated post-fabrication frequency trimming for resonators used for readout and Purcell filtering, greatly enhancing the processor yield through robustness to fabrication and design uncertainty (Appl. Phys. Lett.). On the measurement side, we experimentally demonstrated a hardware-efficient leakage reduction unit for transmons (Phys. Rev. Lett.) previously proposed in 2021 by the Terhal group (PRX Quantum), and showed their application in an error-correction context. Finally, in collaboration with the company Riverlane, we demonstrated the reduction of logical error rates in a distance-three bit-flip surface code by eking out information from the analog readout signal of quantum parity checks (measurements finalized in 2023, submitted for publication in 2024; arXiv).

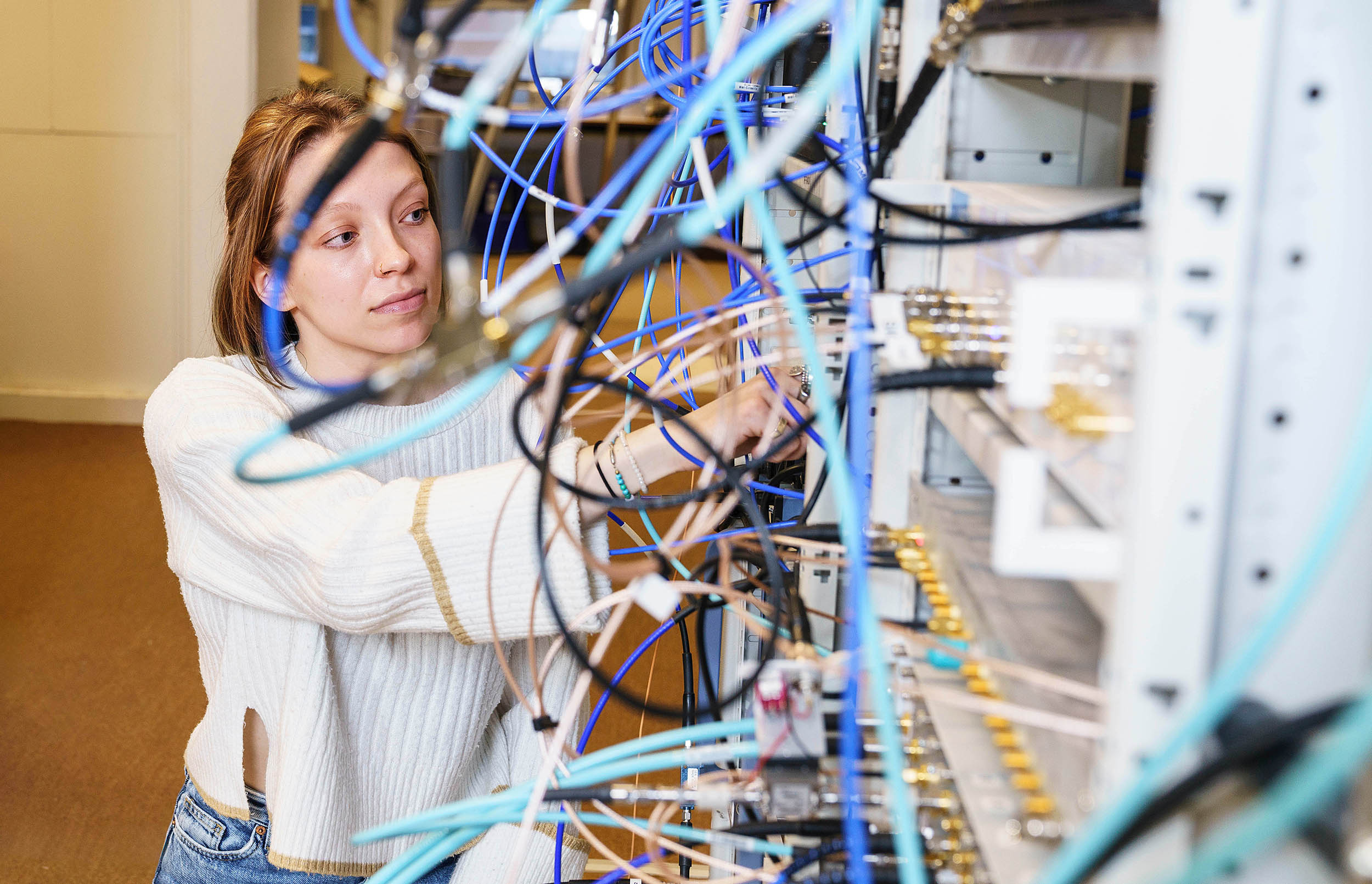

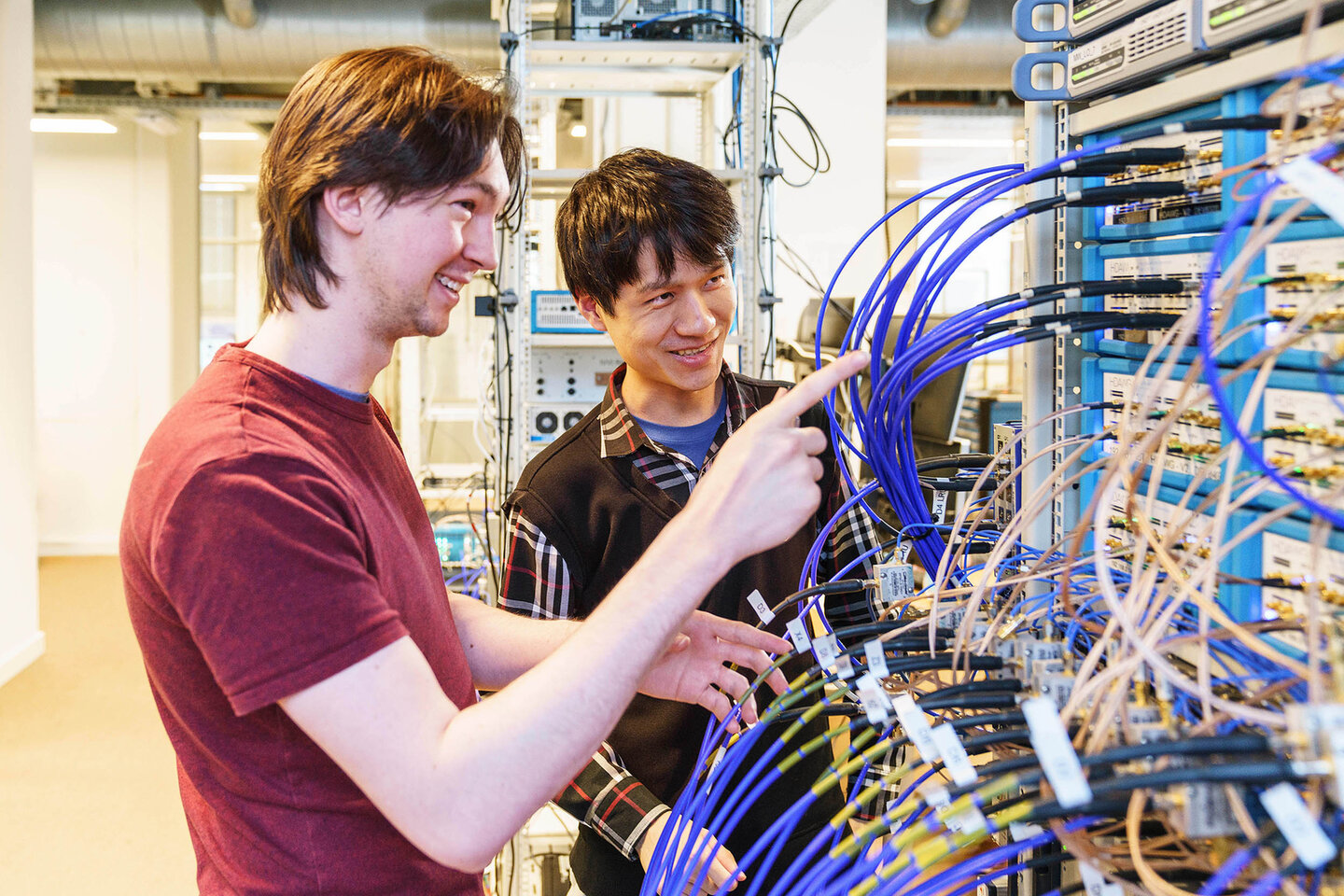

Overall, 2023 has been a year of transition. The IARPA Strong collaborations [funded by QDNL (start May 2023) and the European Flagship consortium OpenSuperQPlus (start March 2023)] have begun with local spin-off companies QuantWare (quantum hardware), Delft Circuits (cryogenic wiring), Qblox (control electronics), and Orange Quantum systems (enabling software), aiming to scale the superconducting backend of Quantum Inspire with key upgrades targeted in mid 2024 and mid 2025. These upgrades constitute two key milestones on the road to the 100-qubit target set by the European Flagship for mid 2026.

Cryogenic electronics

Long-term goal:

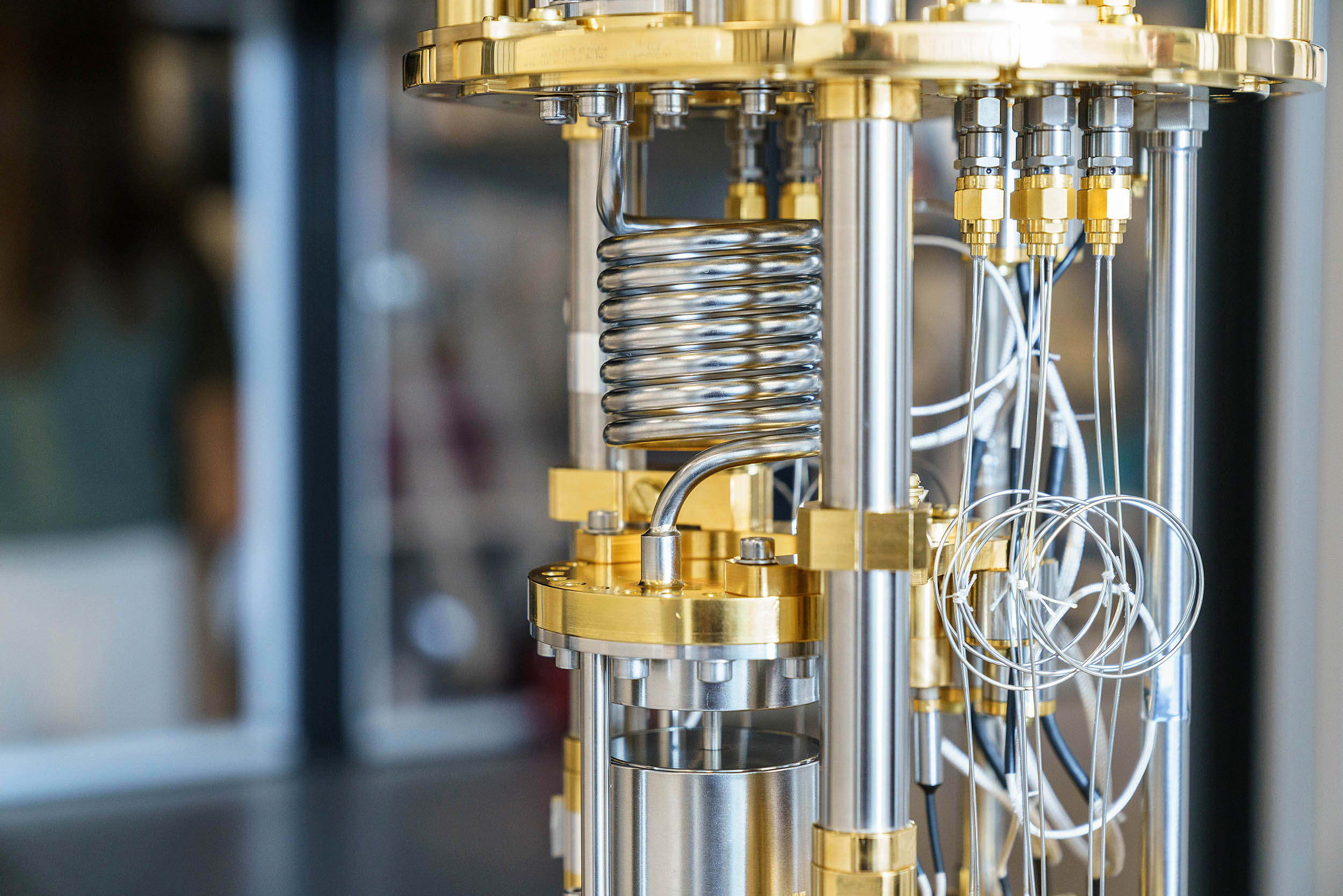

To realize a scalable control framework based on integrated cryogenic electronics that can operate near the qubits, to facilitate large-scale quantum computers.

Highlights

We developed and experimentally demonstrated a family of cryo-CMOS high-speed analog-to-digital converters (TCASI, JSSC), which achieve state-of-the-art performance by handling a bandwidth of up to 500 MHz with less than 2 mW of power dissipation, as required for a compact integrated electronic supporting the frequency-multiplexed RF readout of semiconductor spin qubits. We also devised cryogenic-aware forward body biasing (FBB), a technique for manipulating the threshold voltage of bulk cryo-CMOS transistors aimed at optimizing their performance without any process modification (EDL). We demonstrated its potential by optimizing the speed and power dissipation of both digital circuits and analog components, showing its advantages over commonly used techniques such as adopting FD-SOI CMOS.

We developed critical components for a cryo-CMOS high-speed digital link (MWTL, RFIC), which will enable Gbps communication between room-temperature controllers and the cryogenic quantum processor, a functionality required to transmit input and output data to future large-scale quantum computers. To provide the frequency reference for the qubit control and readout circuits, we developed a calibration technique to minimize the phase noise of cryo-CMOS voltage-controlled oscillators (TCAS-I), and we demonstrated the first cryogenic phase-locked loop (PLL) operating at 4.2 K, able to synthesize 9.4 to 11.6 GHz tones while maintaining high qubit fidelity (JSSC).

Quantum computing architecture stack

Long-term goals:

To develop a scalable quantum computing control system stack that bridges the gap between quantum applications and quantum devices.

Highlights

We constructed a new class of holographic quantum error correction codes which exhibit high thresholds, low-weight transversal logical gates, a simple construction, as well as capturing novel aspects of the AdS/CFT correspondence (Nature Comm.). We developed SpinQ, the first native compilation framework for scalable spin-qubit architectures (ACM Transactions on Quantum Computing). We extended the characterization of quantum circuits by including qubit interaction graph properties using graph theory-based metrics in addition to previously used circuit-describing parameters (Springer Quantum Machine Intelligence).

Quantum Inspire: the multi hardware quantum technology platform

Long-term goals:

To develop a full-stack quantum computer demonstrator for training and education, along with co-development and collaborative R&D of quantum technologies for quantum computing.

Highlights

2023 has been a year of many under-the-hood changes to prepare for Quantum Inspire 2.0, to be launched in 2024. We developed new language definitions supporting many more operations and more user flexibility, and a better fit for quantum compilers. Together with the Faculty of Electrical Engineering, Mathematics and Computer Science we developed a 10x faster emulator for executing quantum circuits, both as vector state simulation and as density matrix simulation.

We also prepared our platform to connect to different backends such as a neutral atom backend, which is scheduled for connection to Quantum Inspire in 2025. Finally, we implemented a functionality to perform hybrid computing with the lowest possible overhead. This allows to run shallow hybrid classical-quantum algorithms and prepares Quantum Inspire for connection with supercomputers to perform even more challenging algorithms.

Figure: Rabi oscillations of a single electron spin at 12 mK (top) and 200 mK (bottom). The oscillations are taken with different wait times between single-shot measurements (see color bar) and scanning the drive time either from left to right, or the other way around. Heating effects cause major differences between these conditions when working at 12 mK. Remarkably, all curves fall on top of each other at 200 mK. Graphs reproduced from Phys. Rev. X.

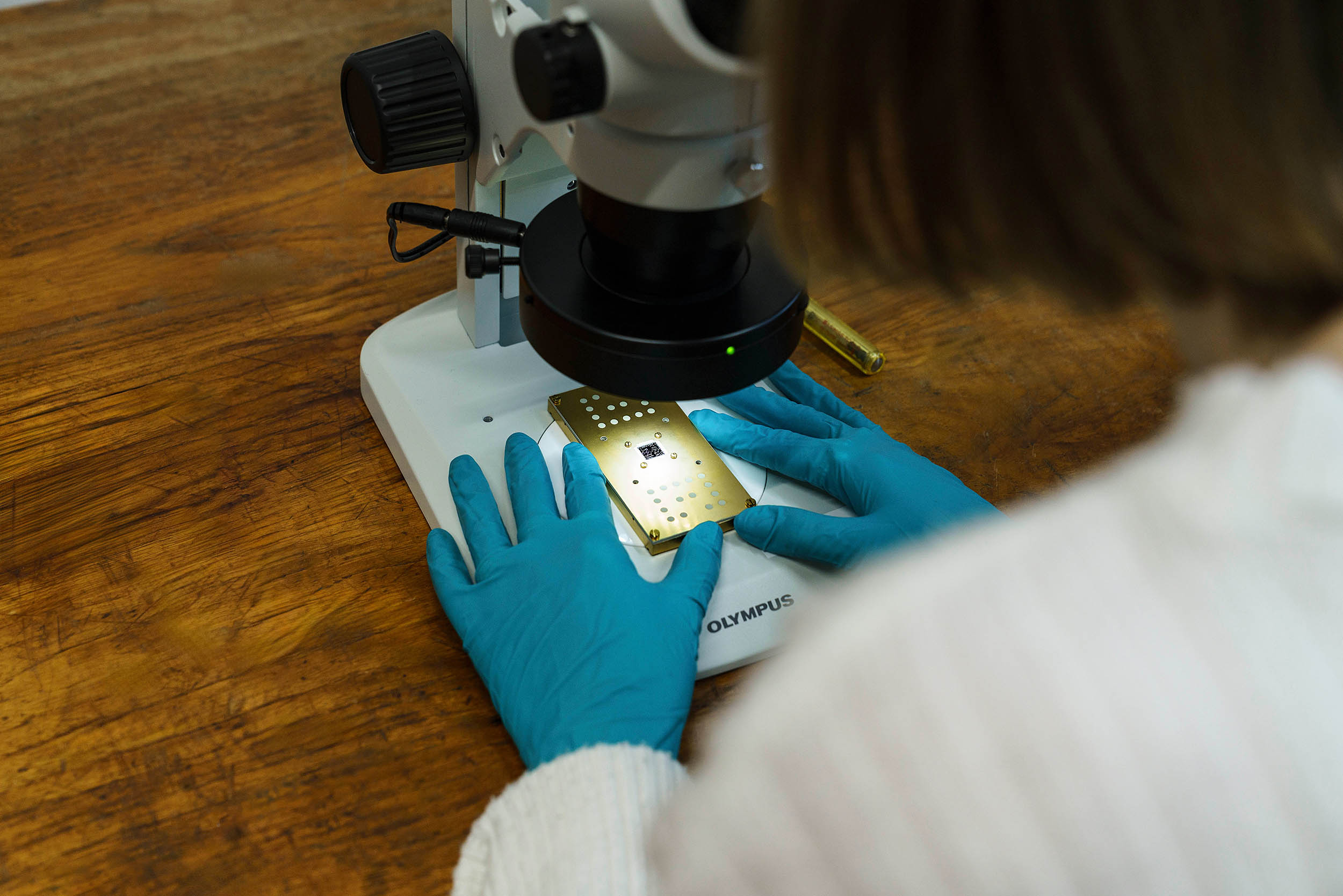

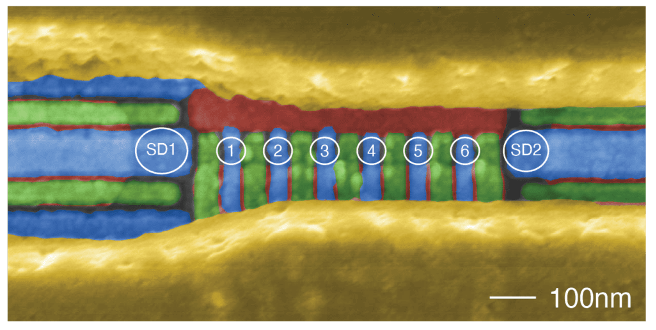

Image of the six-qubit quantum processor described in this article (Nature). The qubits are created by tuning the voltage on the red, blue, and green wires on the chip. The structures called SD1 and SD2 are extremely sensitive electric field sensors, which can even detect the charge of a single electron. These sensors together with advanced control schemes allowed the researchers to place individual electrons at the locations labeled (1)-(6), which were then operated as qubits.